| Α | Υ | 21 |  |

|---|---|----|--|

QP Code: RM21BTECH439 Reg. No

## GIET UNIVERSITY, GUNUPUR - 765022

B. Tech (Sixth Semester Regular) Examinations, May - 2024

## 21BECPC36001 - Digital VLSI Design

(ECE)

| T        | ime: 3 hrs                                                                                                                                                                                                                                                                                                                                                                 | <b>A</b> aximur | n: 70 M                           | arks            |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------|-----------------|--|

|          |                                                                                                                                                                                                                                                                                                                                                                            |                 | $(2 \times 5 = 10 \text{ Marks})$ |                 |  |

| Q.1.     | Answer ALL questions                                                                                                                                                                                                                                                                                                                                                       |                 | CO#                               | Blooms<br>Level |  |

| a. :     | Explain bottom up approach in VLSI design.                                                                                                                                                                                                                                                                                                                                 |                 | CO1                               | K1              |  |

| b. :     | Draw the symbol of enhancement and depletion type of n-MOSFET.                                                                                                                                                                                                                                                                                                             |                 | CO1                               | K2              |  |

| c.       | What is parasitic capacitance in CMOS circuit?                                                                                                                                                                                                                                                                                                                             |                 | CO2                               | К3              |  |

| d.       | What is interconnect delay in VLSI circuit?                                                                                                                                                                                                                                                                                                                                |                 | CO3                               | К3              |  |

| e.       | Draw the nMOS pass transistor, and explain its working.                                                                                                                                                                                                                                                                                                                    |                 | CO4                               | К3              |  |

| PART – B |                                                                                                                                                                                                                                                                                                                                                                            | (15 x           | 4 = 60 N                          | (Jarks          |  |

| Answ     | ver ALL questions                                                                                                                                                                                                                                                                                                                                                          | Marks           | CO#                               | Blooms<br>Level |  |

| 2. a.    | What is oxidation and photolithography in semiconductor fabrication industry? Discuss the quality of oxide and method of photolithography.                                                                                                                                                                                                                                 | 7               | CO1                               | K2              |  |

| b.       | Explain top down approach for VLSI logic circuit design. (OR)                                                                                                                                                                                                                                                                                                              | 8               | CO1                               | K3              |  |

| c.       | What is stick diagram? Draw an enhancement type load (nMOS) inverter circuit and design its stick diagram.                                                                                                                                                                                                                                                                 | 7               | CO1                               | K2              |  |

| d.       | Explain each step of fabrication for n-MOSFET,                                                                                                                                                                                                                                                                                                                             | 8               | CO1                               | К3              |  |

| 3.a.     | Explain the working principle of p-MOSFET for different gate bias condition. Draw its cross-sectional view to explain its region of operation.                                                                                                                                                                                                                             | 10              | CO2                               | K4              |  |

| b.       | What are the advantages of dynamic logic circuit?                                                                                                                                                                                                                                                                                                                          | 5               | CO2                               | K4              |  |

|          | (OR)                                                                                                                                                                                                                                                                                                                                                                       |                 |                                   |                 |  |

| c.       | Calculate the threshold voltage $V_{TH}$ at $V_{SB} = 0$ , for a polysilicon gate n-channel MOSFET. Substrate doping density $N_A = 10^{16}$ cm <sup>-3</sup> , polysilicon gate doping density $N_D = 2 \times 10^{20}$ cm <sup>-3</sup> , gate oxide thickness $t_{ox} = 500$ Å, and oxide-interface fixed charge density $N_{ox} = 4 \times 10^{10}$ cm <sup>-2</sup> . | 10              | CO2                               | K3              |  |

| d.       |                                                                                                                                                                                                                                                                                                                                                                            | 5               | CO2                               | K4              |  |

| 4.a.     | Draw the clocked CMOS SR-latch circuit based on NAND gate and explain its function and write the corresponding truth table.                                                                                                                                                                                                                                                | 10              | CO3                               | K4              |  |

| b.       | type load.                                                                                                                                                                                                                                                                                                                                                                 | 5               | CO3                               | K5              |  |

|          | (OR)                                                                                                                                                                                                                                                                                                                                                                       | 4.0             | 002                               | 77.4            |  |

| c.       | Draw the circuit diagram for CMOS D-Latch using transmission gate and explain its working.                                                                                                                                                                                                                                                                                 | 10              | CO3                               | K4              |  |

- d. What is transmission gate? Implement the Boolean expression  $X\overline{Y}+XY$  using 5 transmission gate.

- 5.a. What is voltage Bootstrapping. Explain bootstrapping technique by considering 10 CO4 K5 an inverter (with enhancement type nMOS load with unknown voltage Vx at gate terminal) circuit and find ratio of boot capacitor and source-to-substrate capacitance.

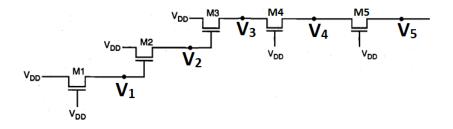

- b. Observe the given circuit and find the voltage V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>, V<sub>4</sub>, and V<sub>5</sub>. Consider 5 the threshold voltage for nMOS transistor M1, M2, M3, M4, and M5 as V<sub>TH1</sub>, V<sub>TH2</sub>, V<sub>TH3</sub>, V<sub>TH4</sub>, and V<sub>TH5</sub> respectively.

(OR)

- c. What is precharge and evaluate in Dynamic logic circuit? Using this technique, 10 CO4 K5 draw and explain the working of dynamic CMOS circuit for the Boolean expression (A<sub>1</sub> · A<sub>2</sub> · A<sub>3</sub>)+(B<sub>1</sub> · B<sub>2</sub>).

- d. What is domino CMOS logic? Explain with example. 5 CO4 K4

--- End of Paper ---