|                                   |  |     |  | 1 |  | 1 | 1 |  | 1 1 |      |

|-----------------------------------|--|-----|--|---|--|---|---|--|-----|------|

| Registration No.:                 |  |     |  |   |  |   |   |  |     |      |

| Total number of printed pages – 3 |  |     |  |   |  |   |   |  |     | В. Т |

| 10tarriani                        |  | , , |  |   |  |   |   |  | _   |      |

ech

PCEC 4401

## Seventh Semester (Special) Examination - 2013 VLSI DESIGN

BRANCH: EC, IEE, AEIE, ETC

QUESTION CODE: D 383

Full Marks - 70

Time: 3 Hours

Answer Question No. 1 which is compulsory and any five from the rest. The figures in the right-hand margin indicate marks.

Answer the following questions: 1.

2×10

- (a) What is standard cell-based design methods

- An nMOS transistor has a threshold voltage, V<sub>Th</sub> + 0.4 V and a supply voltage, V<sub>DD</sub> = 1.2 V. A circuit designer is evaluating the proposal to reduce by 100 mV to obtain faster transistor. See that factors yould the saturation current increase (at  $V_{GS} = V_{DS} = V_{DD}$ ) if the transistor were ideal?

- Draw the circuit diagram and the corresponding stick diagram of a 4-input (c) NOR gate using CMOS technology.

- What is the minimum power supply voltage required for a CMOS inverter so (d) that it can operate properly?

- Sketch a transistor level schematic for a single-stage CMOS logic for the (e) function  $Y = A \cdot B + C \cdot (A + B)$ .

- State two advantages and two disadvantages of complementary logic. (f)

- Implement a 2-input NAND gate using pass transistor logic. (q)

- What is a tri-state device and what can it be used for ? (h)

- (i) Discuss the solution of cascading problem in the dynamic logic.

- (j) In a DRAM what is the main significance to precharge the bit-lines up to  $(V_{DD}/2)$  instead of  $V_{DD}$ ?

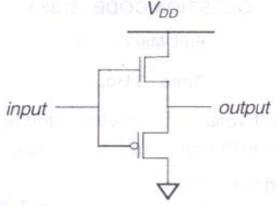

- (a) Consider a non-inverting buffer shown in Figure Q2(a) below that uses an nMOS to pull up and a pMOS to pull down. The nMOS and pMOS transistors have a threshold voltage V<sub>Th</sub> = 0.2 V. The supply voltage is V<sub>DD</sub> = 1.2 V. Determine the HIGH and LOW voltages at the output and thereby the output swing.

Figure Q2(a)

- (b) Why the transient response of the 2-input NOR gate is slower than that of the equivalent inverter 2

- (a) Explain the working of an n-channel enhancement type MOSFET after application of gate bias, with the source and substrate at ground potential and the drain-to-source voltage is initially zero.

- (b) With the help of a neat sketch explain in brief the basic steps of the VLSI design flow.

- 4. What are DC voltage transfer characteristics and noise margins? How do noise margins change with increase in the p-transistor width relative to that of n-transistor? Show that for a symmetric CMOS inverter.

2

$$\left(\frac{W}{L}\right)_p \approx 2.5 \left(\frac{W}{L}\right)_n$$

5. Give the schematic of XILINX Configurable Logic Block (CLB). (a) 5 Write the VHDL code for a 4-to-1 multiplexer. (b) 5 6. Give a brief description of each of the following terms: (a) 5 (i) HDL BIST (ii) State two CAD Tools and describe their use in brief. (b) 5 What are the four key DRAM timing parameters? Write at least two main 7. (a) advantages and disadvantages of DRAM cell? As a VLSI designer what are the techniques you propose to adopt for (b) reducing active power dissipation in the SRAM cell? What is gated-VDD structure in CMOS SRAM to reduce leakage current/power? 8 Answer any **two** of the following: 5×2 Mat are the What is SOI ? What is the material used as psulator advantages and disadvantages of SOI process.? Write the expression for the threshold voltage a MOS vansistor and explain in your own words why the magnitude of thour shold voltage increases as the magnitude of the source-bulk voltage increases (The source-bulk pn diode remains reversed biased.) (c) With the help of a neat circuit diagram show the implementation of the logic function  $Y = A + (B + C) \cdot (D + E)$  using domino CMOS logic. Discuss in brief the fault models for testing of an IC.