| I |   |  |  |   |  |

|---|---|--|--|---|--|

| I |   |  |  |   |  |

| I |   |  |  |   |  |

|   |   |  |  |   |  |

| I |   |  |  |   |  |

| I |   |  |  |   |  |

| I |   |  |  |   |  |

| 1 | 1 |  |  | l |  |

| I |   |  |  |   |  |

## Registration no:

Total Number of Pages: 02 B.TECH

**PCEC4401**

# 7<sup>th</sup> Semester Regular / Back Examination 2015-16 VLSI DESIGN

**BRANCH: AEIE,EC,ETC,IEE**

Time: 3 Hours

Max marks: 70

**Q.CODE: T188**

# Answer Question No.1 which is compulsory and any five from the rest.

### The figures in the right hand margin indicate marks.

| Q1 | a) | Answer the following questions: Show the basic structure of a MOS transistor.                                                    | (2 x 10) |  |  |  |  |

|----|----|----------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|    | b) | What are the three regions of operation of a MOS transistor?                                                                     |          |  |  |  |  |

|    | c) | What is Body effect?                                                                                                             |          |  |  |  |  |

|    | d) | What is the use of the LOCOS technology? Mention its pros and cons.?                                                             |          |  |  |  |  |

|    | e) | Define propagation Delay time with suitable illustration.                                                                        |          |  |  |  |  |

|    | f) | What is the importance of monolithic integration?                                                                                |          |  |  |  |  |

|    | g) | What are the drawbacks of resistive load inverter? How can they be                                                               |          |  |  |  |  |

|    |    | overcome?                                                                                                                        |          |  |  |  |  |

|    | h) | Sketch a transistor level schematic of a CMOS 3-input XOR gate. Assume                                                           |          |  |  |  |  |

|    |    | that both the true and complementary versions of the inputs are available.                                                       |          |  |  |  |  |

|    | i) | Write down at least two advantages and two disadvantages of the pseudo-                                                          |          |  |  |  |  |

|    |    | <i>n</i> MOS logic compared to the CMOS logic.                                                                                   |          |  |  |  |  |

|    | j) | Give the schematic of XILINX Configurable Logic Block (CLB).                                                                     |          |  |  |  |  |

| Q2 | a) | Compare the constant field and constant voltage scaling approaches in                                                            | (5)      |  |  |  |  |

|    |    | terms of area, delay, energy and power density parameters.                                                                       |          |  |  |  |  |

|    | b) | Draw a neat sketch of the <i>Y-chart</i> (or the Gajski Chart) to illustrate the                                                 | (5)      |  |  |  |  |

|    |    | VLSI design domains.                                                                                                             |          |  |  |  |  |

| Q3 | a) | What are DC voltage transfer characteristics and noise margins? How do                                                           | (5)      |  |  |  |  |

|    |    | noise margins change with increase in the p-transistor width relative to that                                                    |          |  |  |  |  |

|    |    | of n-transistor?                                                                                                                 |          |  |  |  |  |

|    | b) | Write briefly the limitations of scaling in MOS VLSI design.                                                                     | (5)      |  |  |  |  |

|    |    |                                                                                                                                  |          |  |  |  |  |

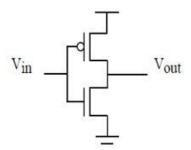

| Q4 |    | Consider the CMOS inverter circuit in Figure Q4 with the following                                                               | (10)     |  |  |  |  |

|    |    | parameters. Assume long channel transistors and no velocity saturation.                                                          |          |  |  |  |  |

|    |    | Given- $V_{DD}$ =3.3 V, $k_n$ =200 $\mu$ A/V <sup>2</sup> , $k_p$ =80 $\mu$ A/V <sup>2</sup> , $V_{T0n}$ =0.6V, $V_{T0p}$ =0.7V. |          |  |  |  |  |

|    |    |                                                                                                                                  |          |  |  |  |  |

Find VOL, VOH, VIL, and VIH on the VTC. Also find the noise margins of this inverter.

- **Q5** a) Implement the equation X = ((A'+B')(C'+D'+E')+F')G' using (5) complementary CMOS using minimum number of transistors. **b)** A polysilicon trace that is 0.6µm wide, 0.05mm long, and 0.5µm thick has (5) a sheet resistance of  $20\Omega$ . It is used to form a high frequency signal trace. i) What is sheet resistance? Calculate the resistance of the poly trace. ii) Calculate the line capacitance of this signal trace assuming the line is separated from a conducting plate by a 100Å thick oxide layer. Express your answer in fF (10-15) iii) Calculate the time constant (RC-delay) associated with this trace. What does this result indicate? **Q6** a) If a domino gate input is initially a '1' at the start of evaluation, can it make (5) any other transition during evaluation? Why or Why not? Explain briefly, how as a VLSI designer you can optimize the performance of domino logic circuits? Illustrate a domino logic circuit. **b)** Explain in brief the meanings of regularity, modularity and locality with (5) reference to VLSI design. What is hierarchy in design? **Q7** a) Draw a 1 T DRAM memory cell. What are the advantages of using address (5)

- **b)** In a DRAM what is the main significance to precharge the bit-lines up to  $V_{DD}/2$  instead of  $V_{DD}$ ? What are the main differences between 1-T DRAM cell and 3-T DRAM cell?

(5)

multiplexing scheme in DRAM cell? What are the four key DRAM timing

#### Q8 Write short notes on any two: (5 x 2)

- a) CMOS Inverter VTC

- **b)** LOCOS technique

parameters?

- c) BIST

- d) CMOS Implementation of SR Latch