|                                                                                                                     |                                                                                                                                                  | Re                     | gistration no:                                                                                                                                                                                                                                                                                                            |                                |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|--|--|--|--|--|

| 210                                                                                                                 | Tota                                                                                                                                             | 21<br>al Nu            | mber of Pages: 03                                                                                                                                                                                                                                                                                                         | 210<br><u>B.TECH</u><br>E4I103 |  |  |  |  |  |  |  |  |

| 4 <sup>th</sup> Semester Regular / Back Examination 2017-18<br>DIGITAL ELECTRONICS CIRCUIT<br>BRANCH(S): ELECTRICAL |                                                                                                                                                  |                        |                                                                                                                                                                                                                                                                                                                           |                                |  |  |  |  |  |  |  |  |

| 210                                                                                                                 |                                                                                                                                                  | 21                     | <sup>210</sup> BRANCH(S): ELECTRICAL<br>Time: 3 Hours <sup>210</sup> <sup>210</sup> <sup>210</sup> <sup>210</sup><br>Max marks: 100<br>Q.CODE:C772                                                                                                                                                                        | 210                            |  |  |  |  |  |  |  |  |

|                                                                                                                     | Answer Question No.1 & Question No.2 which are compulsory and any<br>four from the rest.<br>The figures in the right hand margin indicate marks. |                        |                                                                                                                                                                                                                                                                                                                           |                                |  |  |  |  |  |  |  |  |

| 210                                                                                                                 |                                                                                                                                                  | 21                     |                                                                                                                                                                                                                                                                                                                           | 210                            |  |  |  |  |  |  |  |  |

|                                                                                                                     | Q1                                                                                                                                               | a)                     | The NAND gate output will be low if the two inputs are(A) 00(B) 01(C)10(D) 11                                                                                                                                                                                                                                             | (2 x 10)                       |  |  |  |  |  |  |  |  |

| 210                                                                                                                 |                                                                                                                                                  |                        | A ring counter consisting of five Flip-Flops will have<br>(A) 5 state (B) $2^5$ states (C) $(2)^{25}$ states (D) Infinite states.<br>If the input to T-flipflop is 100 Hz signal, the final output of the three T-flipflops in cascade is<br>(A) 1000 Hz (B) 500 Hz (C) 333 Hz (D) <sup>210</sup> 12.5 Hz. <sup>210</sup> | 210                            |  |  |  |  |  |  |  |  |

|                                                                                                                     |                                                                                                                                                  | d)<br>e)               | $\begin{array}{ll} (734)_8 = ( \ \underline{ \ \ } )_{16} \\ (A) C 1 D & (B) D C 1 & (C) 1 C D & (D) 1 D C \\ \mbox{If J = K (J and K are shorted) in a JK flip-flop, what circuit is made} \\ A. SR flip-flop \\ B. Shorted JK flip-flop \\ C. T flip-flop \end{array}$                                                  |                                |  |  |  |  |  |  |  |  |

| 210                                                                                                                 |                                                                                                                                                  | f) <sup>21</sup><br>g) | D. K flip-flop<br>A device which converts BCD to Seven Segment is called <sup>210</sup> 210<br>(A) Encoder (B) Decoder (C) Multiplexer (D) Demultiplexer<br>The hexadecimal number 'A0' has the decimal value equivalent to                                                                                               | 210                            |  |  |  |  |  |  |  |  |

|                                                                                                                     |                                                                                                                                                  | h)<br>i)<br>j)         | How many Flip-Flops are required for mod-16 counter?<br>(A) 5 (B) 6 (C) 3 (D) 4<br>The Boolean expression A.B' + A'.B + A.B is equivalent to<br>The minimal function that can detect a "divisible by 3" 8421 BCD code digit<br>(representation is $D_8 D_4 D_2 D_1$ ) is given by<br>210 210 210 210 210                  |                                |  |  |  |  |  |  |  |  |

| 210                                                                                                                 |                                                                                                                                                  | 21                     | $\begin{array}{c} (representation   s D_8 D_4 D_2 D_1)   s given by \\ A. D_8 D_1 + D_4 D_2 + D'_8 D_2 D_1 \\ B. D_8 D_1 + D_4 D_2 D'_1 + D'_4 D_2 D_1 + D'_8 D'_4 D'_2 D'_1 \\ C. D_8 D_1 + D_4 D_2 + D'_8 D'_4 D'_2 D'_1 \\ D. D_4 D_2 D'_1 + D_4 D_2 D_1 + D_8 D'_4 D_2 D_1 \end{array}$                               | 210                            |  |  |  |  |  |  |  |  |

| 210                                                                                                                 | Q2                                                                                                                                               |                        | Answer the following questions:<br>2's complement representation of a 16 bit number (one sign bit and 15 magnitude bits) is<br>FFFF. Represent its magnitude in decimal.                                                                                                                                                  | ( <b>2 x 10</b> )              |  |  |  |  |  |  |  |  |

|                                                                                                                     |                                                                                                                                                  | b)<br>c)               | What is race around condition? How to over come to this situation.<br>Draw the flip-flop output waveforms of a 4-bit SISO shift register assuming the initial data stored in the register is 1001?                                                                                                                        |                                |  |  |  |  |  |  |  |  |

|                                                                                                                     |                                                                                                                                                  |                        |                                                                                                                                                                                                                                                                                                                           |                                |  |  |  |  |  |  |  |  |

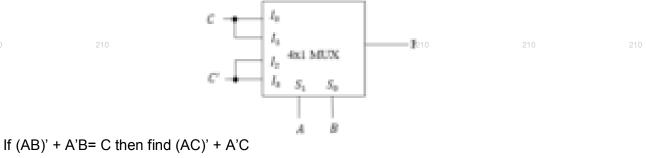

What is the expression for the Boolean Function F in the circuit shown in the figure below? d)

- e)

- What is priority encoder? Write the truth table of 4 input priority encoder. f)

- State the difference between edge triggering and level triggering. g)

- How many numbers of Boolean functions that can be generated by n variables? h)

- Compare the characteristics equation of R-S Flip-Flop with J-K Flip-Flop. i)

- Realize the Boolean expression Y = (x+y)(x+y') using NAND gates. i)

- Design a comparator circuit that compares two '4' bit Numbers A and B With all conditions. (10) Q3 a)

- Find the dual and complement of the following Boolean expression F(x,y,z) =b) (5) x'yz+x'yz'+xy'z'+xy'z

- Implement the Boolean Function  $F(A, B, C, D) = \sum (1,3,4,11,13,14,15)$  using 4X1 MUX? Q4 (10) a)

- Construct a 5-to 32-line decoder with four Nos of 3-to 8-line decoder having enable line b) (5) and a 2- to 4-line decoder. Use block diagram for the components?

- a) A PN flip-flop has four operations: clear to '0', no change, complement and set to '1', when Q5 (8) 210 inputs P and N are 00,01,10,11 respectively. Tabulate the characteristic table and derive the characteristic equation? b) Design a mod 4 synchronous counter using J-K Flip Flop and implement it. (7)

- (8) **Q6** a) With neat sketch, explain the operation of a 3-bit universal shift register

- b) Design a 3 x 8 decoder and Implement it using a suitable PLA.

- The K map for a Boolean function is shown in the figure below. Find out the number of **Q7** a) (10) essential prime implicants for this function?

| AB<br>CD         | 00 | 01    | 11 | 10 |     |

|------------------|----|-------|----|----|-----|

| 00               | 1  | 1     | 0  | 1  |     |

| 01               | 0  | 0     | 0  | 1  |     |

| <b>11</b><br>210 | 1  | 0 210 | 0  | 0  | 210 |

| 10               | 1  | 0     | 0  | 1  |     |

|                  |    |       |    |    |     |

b) With proper block diagram explain SAR type ADC (Analog to Digital Converter) (5)

a) All the logic gates shown in the figure have a propagation delay of 20 ns. Let A=C=0 and **Q**8 (10)B=1 until time t=0. At t=0, all the inputs flip (i.e. A=C=1 and B=0) and remain in that state. For t>o. for how much duration (in ns) the output (z) will be at logic 1. Explain?

(7)

- **b)** Explain the operation of a 8 x 1 Multiplexer and Implement the following function (5) using a suitable Multiplexer

- $^{210}F(A, B, C, D) = \sum m (0, 1, 3, 5, 6, 7, 8, 9, II, 13, 14)$  210

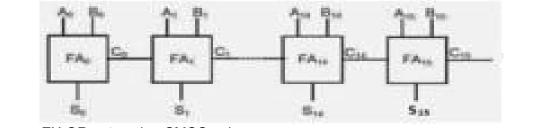

- Q9 a) A 16 bit ripple carry adder is realized using 16 identical full adders (FA) as shown in the figure. The "carry" propagation delay of each FA is 12 ns and the "sum" propagation delay of each FA is 15 ns. Find the worst case delay (in ns) of this 16 bit adder?

(5)

**b)** Design an EX-OR gate using CMOS only.

| 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

| 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

| 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

| 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

|     |     |     |     |     |     |     |     |