**Total Number of Pages: 02**

**B.Tech PEEI5404**

## 8<sup>th</sup> Semester Regular / Back Examination 2016-17 ANALOG VLSI DESIGN

BRANCH(S):CSE, IT, ITE Time: 3 Hours Max Marks: 70

Q.CODE:Z398

Answer Question No.1 which is compulsory and any five from the rest. The figures in the right hand margin indicate marks.

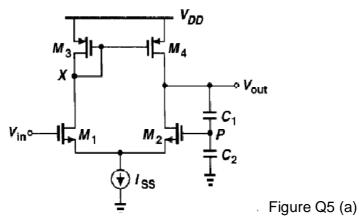

## Q1 (2 x 10) **Answer the following questions:** a) With the aid of a diagram show the various Levels of Abstraction. b) Draw the circuit of the Common Source Stage with its small signal equivalent. c) How can the gain of a Common Source stage be maximized? d) Draw the circuit configuration and the input output characteristics of a Common Source stage with a diode connected load. e) Mention one advantage and one drawback of the CS Stage with Triode Load? f) What is the shielding property? g) What is a folded cascode? **h)** Draw a basic differential pair. Mention some of its use. What is a Gilbert Cell? Mention its use. Draw a Common Gate stage at high frequency and mention one important property of the same. **Q2** a) Discuss the effect of Loading in two port networks. (8)**(2)** b) The output resistance increase due to use of source degeneration? Explain. Q3 a) Draw the equivalent circuit for the Colpitts Oscillator topology. Calculate (3) the voltage gain of the same. **b)** What is a VCO? What are the important parameters of VCO? **(7)** Calculate the input and output impedence of a Source Follower. Q4 (10)**Q5** a) Define PSRR. Calculate the PSRR for the given circuit in Figure Q5 (a). (5)

- b) Discuss the effect of Slewing in OPAMPs.

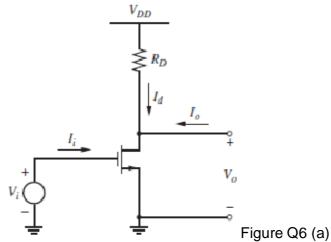

- **Q6** a) Find the voltage gain of the common-source amplifier of Figure Q6 (a)with  $V_{DD}=5V$ ,  $R_D=5k\Omega$ ,  $k'=\mu_nC_{ox}=100\mu\text{A/V}^2$ ,  $W=50\mu\text{m}$ ,  $L=1\mu\text{m}$ ,  $V_f=0.8V$ ,  $L_d=0$ , L=0, and L=0. Assume that the bias value of L=0 value of

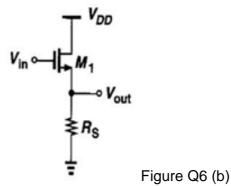

**b)** For the given circuit in Figure Q6 (b), calculate the  $g_m$  and  $A_v$ . Also draw its small signal equivalent model. (5)

- What is the objective of Reference generation? What are the different design issues in Bandgap Reference? (10)

- Q8 Write short answer on any TWO: (5 x 2)

- a) Common-Source Stage with Resistive Load

- b) Differential Pair with MOS Loads

- c) Different types of Amplifier Configurations

- d) LC Oscillator and Ring Oscillator

(5)