| Reg. |  |  |  |  |  |

|------|--|--|--|--|--|

| No   |  |  |  |  |  |

## Gandhi Institute of Engineering and Technology University, Odisha, Gunupur (GIET University)

B. Tech (Sixth Semester - Regular) Examinations, April 2025

21BECPC36001 – Digital VLSI Design

(ECE)

Time: 3 hrs

## Maximum: 70 Marks

| 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | via Annun        | 1. 70 1010         | arks            |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|-----------------|--|--|

|       | Answer ALL questions<br>(The figures in the right hand margin in directs marks)                                                                                                                                                                                                                                                                                                                                                                 |                  |                    |                 |  |  |

| Р     | (The figures in the right hand margin indicate marks)<br>ART – A                                                                                                                                                                                                                                                                                                                                                                                | $(2 \times 5 =$  | (2 x 5 = 10 Marks) |                 |  |  |

|       | Answer ALL questions                                                                                                                                                                                                                                                                                                                                                                                                                            | (_ ~ ~           | CO #               | Blooms          |  |  |

| -     | Define Moore's Law.                                                                                                                                                                                                                                                                                                                                                                                                                             |                  | CO1                | Level<br>K1     |  |  |

|       | Define accumulation and inversion region in MOS capacitor.                                                                                                                                                                                                                                                                                                                                                                                      |                  | C01                | K1<br>K1        |  |  |

|       | Basic difference between a static CMOS and a dynamic CMOS.                                                                                                                                                                                                                                                                                                                                                                                      |                  | CO4                | K2              |  |  |

|       | What is the significance of CMOS technology in digital VLSI design?                                                                                                                                                                                                                                                                                                                                                                             |                  | CO4                | K2              |  |  |

| e.    | Define the noise margin and write the expression noise margin high.                                                                                                                                                                                                                                                                                                                                                                             |                  | CO3                | K2              |  |  |

| Р     | ART – B                                                                                                                                                                                                                                                                                                                                                                                                                                         | $(15 \times 4 =$ | 15 x 4 = 60 Marks) |                 |  |  |

| Ansv  | ver All the questions                                                                                                                                                                                                                                                                                                                                                                                                                           | Marks            | CO #               | Blooms<br>Level |  |  |

| 2. a. | Explain the various VLSI design methodologies. Compare and contrast the Ful<br>Custom, Semi-Custom, and Programmable Logic design approaches in terms<br>design time, flexibility, performance, and cost.                                                                                                                                                                                                                                       |                  | CO2                | K4              |  |  |

| b.    | of hierarchy involved in combining individual 1-bit full adders to form the 4-b<br>adder.                                                                                                                                                                                                                                                                                                                                                       |                  | CO3                | К4              |  |  |

|       | (OR)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                | 604                | 144             |  |  |

| c.    | Describe the fabrication process flow for manufacturing a VLSI (Very-Larg<br>Scale Integration) chip. Discuss the various steps involved, from wafe<br>preparation to packaging.                                                                                                                                                                                                                                                                |                  | CO1                | К1              |  |  |

| d.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ne               | CO1                | K1              |  |  |

| 3.a.  | Consider a MOS structure comprising a n-type doped silicon substrate, a silico<br>dioxide layer, and a metal gate. The equilibrium Fermi potential of the dope<br>silicon substrate is $q\phi_{Fn} = 0.2$ eV. Electron affinity of silicon and the metal at<br>4.15 and 4.1eV respectively. Calculate the built-in potential difference across th<br>MOS system. Draw the Energy band diagrams of the components that make u<br>the MOS system. | ed<br>re<br>ne   | CO1                | К1              |  |  |

| b.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                | CO2                | КЗ              |  |  |

|       | (OR)                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                    |                 |  |  |

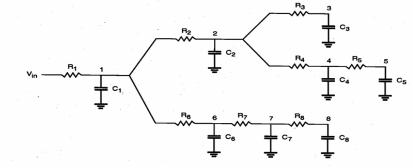

| c.    | Design the combinational logic circuit $Y = \overline{A.B.C}$ using CMOS technology                                                                                                                                                                                                                                                                                                                                                             | 5                | CO4                | К6              |  |  |

| d.    | Write the code of SR FF using Verilog code                                                                                                                                                                                                                                                                                                                                                                                                      | 10               | CO4                | К6              |  |  |

| 4.a.  | Explain working principle of CMOS transmission gate and find effective resistance of three different region                                                                                                                                                                                                                                                                                                                                     | /e 8             | CO4                | К4              |  |  |

| b.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                | CO3                | K4              |  |  |

- (OR)

- c. Consider a CMOS inverter circuit with the following parameters: VDD =3.3 V 8 CO3 K4  $V_{T,n}$ =0.6V, $V_{T,p}$  =-0.7 V  $k_n$  = 200 µA/V2  $k_p$ = 80 µA/V2 (5.83) (5.84) Calculate the noise margins of the circuit.

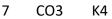

- d. Find the Elmore delay at node 1 node 7

- 5.a. Draw the CMOS SR-Latch circuit based on NAND gate and explain its function 10 CO4 K2 and write the corresponding truth table

- b. Find an equivalent  $(W/L)_P$  and  $(W/L)_n$  of CMOS inverter circuit for simultaneous 5 CO3 K3 switching of all inputs, assuming that  $(W/L)_P = 5$  for all pMOS transistors and (W/L) = 6 for all nMOS transistors.

- c. Explain the voltage bootstrapping method and discuss the need for bootstrapping, 10 CO3 K4 illustrate the working with a suitable circuit diagram, and derive the expression for the capacitor ratio  $\frac{C_{boot}}{C_r}$

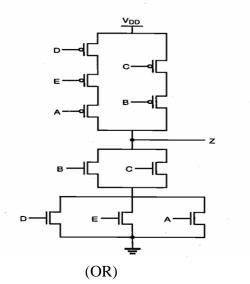

- d. Observe the given circuit and find the voltage V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>, V<sub>4</sub>, and V<sub>5</sub>. Consider 5 CO3 K4 the threshold voltage for nMOS transistor M1, M2, M3, M4, and M5 as V<sub>TH1</sub>, V<sub>TH2</sub>, V<sub>TH3</sub>, V<sub>TH4</sub>, and V<sub>TH5</sub> respectively.

--- End of Paper ---